Build Instructions

General Setup (Do This First!)

- Some software which is necessary before using our morse code decoder are gtkwave for viewing the results of simulation done of the device done with Icarus Verilog as well as Vivado in order to implement the hardware design on an FPGA. Note that in our testing we used the Zybo

Zynq-7000 ARM/FPGA SoC Trainer Board and the Diligent Pmod8LD attachment in the JE PMOD plug of the FPGA.

- After downloading the necessary software go out GitHub repository and clone the

master and FPGA branches.

Simulation

- Switch to the

master branch of the repository.

- See instructions in

MorseDecoder.t.v to change what you want to be communicated through Morse code.

- Run

make run to compile and run the simulation.

- Run

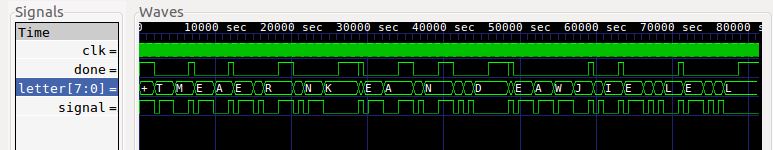

gtkwave Decoder.vcd in the terminal to open the simulation results in gtkwave, and view the letter and done signal to identify the letters which were transmitted and should theoretically

be visible to the user. Optionally one can use the letter filter in the /filters directory in the root of the repository to translate the ASCII codes for letters to their actual characters. Example output for this is shown below:

Notice how the letter signal spell “Mark and Jill” if you read it where it coincides with a high

Notice how the letter signal spell “Mark and Jill” if you read it where it coincides with a high done signal.

- Optionally, run other test benches for other modules by following instructions in

Makefile on the master branch.

FPGA Implementation On Zybo Zynq-7000

- Switch to the

FPGA branch in the project repository

- Plug in the FPGA and turn in on.

- Launch Vivado and select “Create Project”

- On the Project Type screen, keep default options intact.

- On the Default Part screen, click “Boards” and select Zybo if you are using the same board referenced in General Setup. Alternativly if you did not install the board files) you can search for the board under “Parts”.

- Take the

ZYBO_Master.xdc file from the repository and click “Add Sources” and select “Add or create constraints”. Select the XDC file, and check “Copy constraints file into project”.

- Expand Constraints, and double clock

ZYBO_Master.xdc to edit it. Everything is commented (disabled) initially, and you can uncomment elements as needed for your design

by deleting the #. For our project we want the clk set property line, and those for the button, LEDs, and the JE PMOD to be uncommented.

- Next select “Add Sources” and then “Add or create design sources”. Here we need to include the following files:

DitDahDecoder.v, MorseDecoder.v, alphabetMachine.v, morse_wrapper.v,

and register.v.

- Next, perform Synthesis, Implementeation, and Generate Bitstream in order.

- Open the Hardware Manager and click “Open Target” and then “Autoconnect”.

- Lastly, click “Program Device” and enjoy!

Notice how the letter signal spell “Mark and Jill” if you read it where it coincides with a high